# PCI Express Gen 1/2/3/4 Phy IP Core

### Description

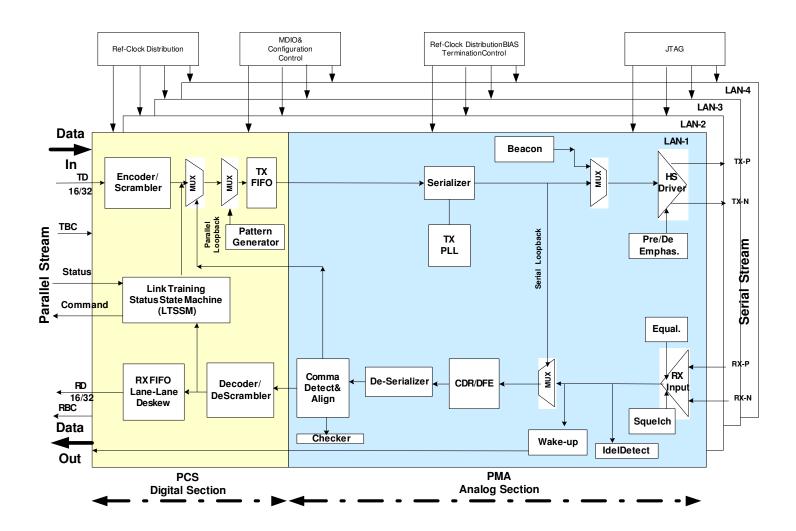

The TRC16024CPA is a four lane Gen 1,2,3,4 PCI Express Physical layer (Phy) Phy IP core, delivering high-speed serial data transmission over controlled impedance transmission media such as copper cable, PCB traces or fiber optics. The device offers support for 2.5/5.0/8.0/16 Gbps PCI Express which include spread spectrum clocking, beacon out of band signaling and deemphasis support. TRC16024CPA operates on 0.8/1.8 V supplies. The IP is capable of transmitting and receiving serial data at 2.5,5.0,8.0,16 Gbps per lane with excellent bit error rate performance.

Each transmit section of the TRC16024CPA contains a low-jitter clock synthesizer, a parallel to serial converter with built in PCS transmit functions, and a CMOS output driver with selectable de-emphasis for use in backplane applications.

Each receive section contains an input limiting amplifier with on-chip terminations and selectable equalization levels, clock/data recovery PLL, and PCS receive functions. Built-in serial and parallel loopback modes. PRBS generator/checker and error detectors aid in support of testing.

The TRC16024CPA requires no external components for its clock synthesizers and clock recovery PLL. Three external resistors are needed to set the proper bias currents for its on-chip terminations.

TRC16024CPA has low jitter generation and high jitter tolerance making it ideal for integration in SoCs and ASICs in the presence of multiple clocks and noise. TSMC is available in TSMC

16 nm FFC process and can be ported to other processes.

#### **Features**

- 2.5/5.0/8/16 Gbps per lane interface optimized for PCI Express applications

- Compliance to PCI Express 1.0a, 1.1 and 2.1, 3.1 and 4.0 PIPE specifications

- Beacon out of band signaling

- Rate negotiation

- Spread Spectrum Clocking (SSC)

- Receiver detection sequence

- High-speed differential reference clock

- Jitter Tolerance and Jitter generation exceeds the PCI Express Phy spec.

- Programmable output swing and de-emphasis

- Programmable serial input equalization

- interface

- Termination auto calibration on power up

- High speed serial CMOS output drivers with internal terminations

- High speed serial CMOS input stage with internal terminations

- Synchronization for character alignment

- Local and remote loopbacks

- Pseudo-Random (PRBS) pattern generator and error checker to support BIST

- Transmitter electrical idle, and receiver electrical idle detection

- 0.8/1.8V ±5% supplies

- 125 mW max power/lane

- power management modes

- Supports Flip Chip Packaging

- TSMC advanced 16 nm FFC CMOS process

- Available in 1X, 4X, 8X, and 16X configuration

### **Applications**

PCI Express Host Serial ATA Bridge PCI Express Switch PCI-PCI Express Bridge PCI Express End Point Infiniband Bridge PCI Express Add-in Card ON chipset

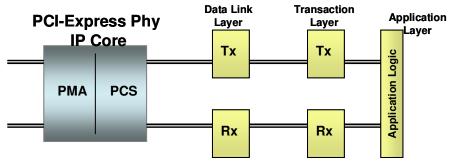

Figure 1. PCI Express Protocol Layer Overview

# PCI Express Gen 1/2/3/4 Phy IP Core

Figure 2. Functional block diagram